# **PX1-C441**

# PCIe/104 OneBank<sup>™</sup> Intel<sup>®</sup> Atom<sup>™</sup> E3900 Single Board Computer with Dual Ethernet

# Product Manual

# **Revision History**

| Document<br>Version | Last Updated<br>Date | Brief Description of Change                       |

|---------------------|----------------------|---------------------------------------------------|

| v1.0                | 7/1/2021             | Initial release                                   |

| v1.01               | 2/24/2022            | Removed references to high temperature grade DRAM |

# **Copyright and Trademarks**

Copyright 2022, WINSYSTEMS, Inc.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of WINSYSTEMS, Inc. The information in the document is subject to change without notice. The information furnished by WINSYSTEMS, Inc. in this publication is believed to be accurate and reliable. However, WINSYSTEMS, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. WINSYSTEMS, Inc. makes no warranty of merchantability or fitness for any purpose. WINSYSTEMS, Inc. assumes no responsibility for any errors that may appear in this document.

#### **Trademark Acknowledgments**

WINSYSTEMS is a registered trademark of WINSYSTEMS, Inc.

Intel and Intel Atom are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

DisplayPort, the DisplayPort logo, and VESA are trademarks owned by the Video Electronics Standards Association (VESA) in the United States and other countries.

Duo-Clasp and Pico-Clasp are trademarks of Molex, Inc.

PC/104 and OneBank are trademarks of the PC/104 Consortium.

All other marks are the property of their respective companies.

# **Table of Contents**

| 1 | <b>Befo</b><br>1.1 |                | Begin                                                                              |   |

|---|--------------------|----------------|------------------------------------------------------------------------------------|---|

| 2 | Intro              | oduction       |                                                                                    | 6 |

| 3 | Fund               | ctionalit      | y                                                                                  | 6 |

| 4 | Feat               | ures           |                                                                                    | 7 |

| 5 | <b>Gen</b><br>5.1  |                | eration                                                                            |   |

| 6 | Spe                | cificatio      | ns10                                                                               | D |

| 7 | Con                | figuratio      | on1                                                                                | 1 |

|   | 7.1                | Compor         | 1°nent Layout                                                                      | 1 |

|   |                    | •<br>7.1.1     | Top View                                                                           |   |

|   |                    | 7.1.2          | Bottom View                                                                        |   |

|   | 7.2                | PCI Dev        | vices and Functions                                                                | 4 |

|   | 7.3                |                | log Timer (WDT)                                                                    |   |

|   | 7.0                | 7.3.1          | WDT Register Usage                                                                 |   |

|   | 7.4                |                | ne Clock/Calendar                                                                  |   |

|   |                    |                | -                                                                                  |   |

|   | 7.5                |                | tors                                                                               |   |

|   |                    | 7.5.1          | J17 - VIN Power Connector                                                          |   |

|   |                    | 7.5.2          | J15 - CMOS Battery Input                                                           |   |

|   |                    | 7.5.3<br>7.5.4 | J10 - SATA Power Output.         12           J1 - LVDS Backlight Power         12 |   |

|   |                    | 7.5.5          | J26 - Power Button                                                                 |   |

|   |                    | 7.5.6          | J25 - Reset Button                                                                 |   |

|   |                    | 7.5.7          | LPDDR4 Memory                                                                      |   |

|   |                    | 7.5.8          | eMMC Onboard                                                                       |   |

|   |                    | 7.5.9          | J9 - M.2 Connector (B Key)                                                         | 9 |

|   |                    | 7.5.10         | J8 - SATA 3 (6 Gbps)                                                               |   |

|   |                    |                | J2 - Mini DisplayPort++ 20                                                         |   |

|   |                    |                | J6 - LVDS Data and HD Audio                                                        |   |

|   |                    | 7.5.13         | BZ1 - Buzzer Speaker                                                               | 1 |

|     |      | 7.5.14 J3 and J4 - LAN Ethernet Ports                                | 21 |

|-----|------|----------------------------------------------------------------------|----|

|     |      | 7.5.15 J5 - USB 2.0 Ports                                            |    |

|     |      | 7.5.16 J11 - USB 3.2 Gen 1 Type-C                                    |    |

|     |      | 7.5.17 J13 - Serial Ports 1–4                                        |    |

|     |      | 7.5.18 J16 - GPIO24 General-Purpose Input/Output                     |    |

|     |      | 7.5.19 J12 - PCle OneBank                                            |    |

|     | 7.6  | Jumpers                                                              | 27 |

|     |      | 7.6.1 JP1 - LVDS Voltage Select                                      | 27 |

|     |      | 7.6.2 JP2 - M.2 Device Type Select                                   |    |

|     |      | 7.6.3 JP4 - Backlight Voltage Select                                 |    |

|     |      | 7.6.4 JP7 - CMOS Clear                                               |    |

|     | 7.7  | LED Indicators D3 - D35                                              | 28 |

| 8   | BIO  | S Functionality                                                      | 28 |

|     | 8.1  | References                                                           | 28 |

|     | 8.2  | Glossary                                                             |    |

|     |      | -                                                                    |    |

|     | 8.3  | BIOS Settings                                                        |    |

|     |      | 8.3.1 Main                                                           |    |

|     |      | 8.3.2         Configuration           8.3.3         Security         |    |

|     |      | 8.3.3         Security           8.3.4         Boot                  |    |

|     |      | 8.3.5 Save and Exit                                                  |    |

|     | 8.4  | Software Description.                                                |    |

|     | •••• | 8.4.1 Software Design Specification: UEFI Operating System Support   |    |

|     |      | 8.4.2 Software Design Specification: Legacy Operating System Support |    |

|     |      | 8.4.3 Software Design Specification: Boot Device Configuration       |    |

|     |      | 8.4.4 Software Design Specification: BIOS Update Mechanisms          |    |

|     |      | 8.4.5 Software Design Requirements: BIOS Components                  |    |

|     | 8.5  | BIOS Update with UEFI Shell                                          |    |

|     |      | 8.5.1 Scope                                                          | 43 |

|     |      | 8.5.2 Process                                                        | 44 |

|     | 8.6  | BIOS Status and Errors                                               | 45 |

|     |      | 8.6.1 BIOS Status and Error Reporting                                | 45 |

|     |      | 8.6.2 Checkpoint Ranges                                              |    |

|     |      | 8.6.3 Standard Checkpoints                                           | 45 |

|     |      | 8.6.4 OEM-Reserved Checkpoint Ranges                                 | 51 |

| 9   | Acce | essories and Cables                                                  | 52 |

| 10  | Soft | tware Drivers                                                        |    |

| • • | 3011 |                                                                      |    |

| A | Best Practices       | 3 |

|---|----------------------|---|

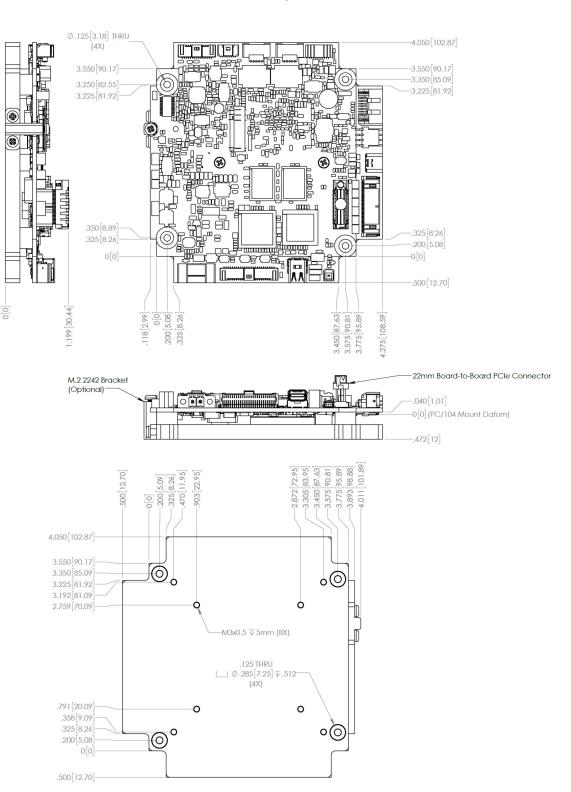

| B | Mechanical Drawings  | 7 |

| C | Warranty Information | 3 |

# 1. Before You Begin

Review the warnings in this section and the best practice recommendations (see "Best Practices" on page 53) when using and handling the WINSYSTEMS PX1-C441. Following these recommendations provides an optimal user experience and prevents damage. Read through this document and become familiar with the PX1-C441 before proceeding.

FAILING TO COMPLY WITH THESE BEST PRACTICES MAY DAMAGE THE PX1-C441 AND VOID YOUR WARRANTY.

#### 1.1 Warnings

Only qualified personnel should configure and install the PX1-C441. While observing best practices, pay particular attention to the following.

#### Avoid electrostatic discharge (ESD)

Only handle the circuit board and other bare electronics when electrostatic discharge (ESD) protection is in place. Having a wrist strap and a fully grounded workstation is the minimum ESD protection required before the ESD seal on the product bag is broken.

# 2. Introduction

This manual provides configuration and usage information for the PX1-C441. If you still have questions, contact Technical Support at (817) 274-7553, Monday through Friday, between 8 AM and 5 PM Central Standard Time (CST).

Refer to the WINSYSTEMS website at http://www.winsystems.com/ for other accessories (including cable drawings and pinouts) that can be used with your PX1-C441.

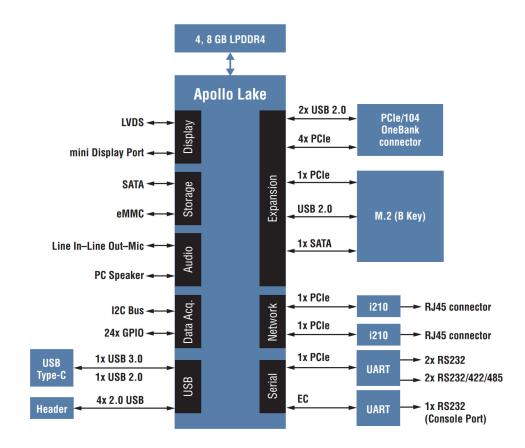

# 3. Functionality

The WINSYSTEMS PX1-C441 single board computer features the Intel<sup>®</sup> Atom<sup>™</sup> Apollo Lake-I Dual core or Quad core system on chip (SOC) for processing and graphics. It includes up to 8 GB of soldered down LPDDR4 system memory and a non-removable eMMC device for solid state storage. In addition, the board supports M.2 and SATA devices.

This full-featured SBC has onboard I/O and supports simultaneous DisplayPort and LVDS video. It provides dual Gigabit Ethernet interfaces, eight USB 2.0 channels, one SuperSpeed USB 3.2 Gen 1 channel, four serial ports and one serial console port, 24 general purpose I/O (GPIO) lines, one I2C bus, stereo audio, and a watchdog timer. Additionally, the board has an M.2 socket and a PCIe/104 OneBank connector that provides four PCIe and two USB 2.0 I/O expansion channels.

NOTE WINSYSTEMS can provide custom configurations for OEM clients. Contact an application engineer for details.

# 4. Features

The PX1-C441 provides the following features.

#### **Single Board Computer**

- Multi-core Intel Atom E3900 processors

- X5 E3930 dual core, up to 1.8 GHz (base frequency 1.3 GHz)

- X5 E3940 quad core, up to 1.8 GHz (base frequency 1.6 GHz)

- X7 E3950 quad core, up to 2.0 GHz (base frequency 1.6 GHz)

#### **Operating Systems (compatibility)**

- Windows 10 x64, IoT Core, and Professional

- Linux x64

- Most x86 operating systems

#### Memory

Up to 8 GB soldered down LPDDR4

#### BIOS

AMI UEFI-compliant BIOS in SPI flash device

#### Video Interfaces (supports dual simultaneous displays)

- Up to 24 bpp color panel support

- Flat-panel resolution up to 1920 x 1200 in dual bus mode

- Low-voltage differential signaling (LVDS)

- Dual Mode Mini DisplayPort++ (version 1.2)

- 4096 x 2160 at 60 Hz

#### Ethernet

- Two Intel 10/100/1000 Mbps controllers using Intel i210

- Wake-on-LAN support, both channels

#### Storage

- One SATA 3.0 (6.0 Gb/s) channel

- One M.2 SSD support (M.2 socket)

- Optional eMMC solid state disk

#### **Digital Input/Output**

24 GPIO bidirectional lines

#### **Bus Expansion**

- PCIe/104 OneBank connection

- Four PCIe channels

- Two USB 2.0 channels

- SATA 3.1 Gen 1 channel

- M.2 B-Key

#### **Serial Interface**

- Two RS232/422/485 serial ports

- Two dedicated RS232 ports

- One RS232 serial console port

- All RS232 ports support RTS/CTS, DTR/DSR, RI, and CD signaling

#### USB

- Eight USB 2.0 ports

- Four USB 2.0 available on USB header

- Two USB 2.0 on PCIe/104 OneBank

- One USB 2.0 on M.2

- USB 3.2 Gen 1 (5 Gbps) port on USB Type-C, with over-current protection

#### Audio

- Hi-definition (HD) audio on DisplayPort interface

- Stereo audio (line in, line out, mic) on LVDS interface

#### Power

- Wide range input power: 9 to 36 VDC

- External battery connector, operates with no battery connected

- +5 V and +12 V SATA power

#### Industrial Operating Temperature

-40 to +85°C (-40 to +185°F)<sup>1</sup>

#### **Additional Features**

- Hardware security Trusted Platform Module (TPM 2.0) enabled

- Watchdog timer adjustable from 1 second to 255 minute reset

- RoHS compliant

1. Requires airflow.

- Backlight power supported

- Custom splash screen on startup

- Intel low-power Gen9 graphics engine

- Intel security engine

# 5. General Operation

#### 5.1 System Block Diagram

WINSYSTEMS' PX1-C441 single board computer (SBC) is a PC/104 form factor SBC with PCIe/104<sup>™</sup> OneBank<sup>™</sup> expansion featuring the latest generation Intel Apollo Lake-I SOC processor. Its small size, rugged design and extended operational temperature make it a great fit for industrial IoT applications and embedded systems in the industrial control, transportation, Mil/COTS, and energy markets.

The SBC is software-compatible with Linux, Windows, and most x86 operating systems, including legacy support for DOS.

Drivers are available from the WINSYSTEMS website.

# 6. Specifications

| The PX1-C441 | adheres to the fo | llowing specifications | and requirements. |

|--------------|-------------------|------------------------|-------------------|

|--------------|-------------------|------------------------|-------------------|

| Feature                     | Specification                                                                                         |  |  |  |  |  |  |  |

|-----------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|                             | Electrical                                                                                            |  |  |  |  |  |  |  |

| V <sub>CC</sub>             | Supports a wide range DC input of 9 to 36 V                                                           |  |  |  |  |  |  |  |

| Models                      | odels PX1-C415-39xx-0-0                                                                               |  |  |  |  |  |  |  |

| Processor                   | E3930 x5 dual core up to 1.8 GHz                                                                      |  |  |  |  |  |  |  |

|                             | E3940 x5 quad core up to 1.8 GHz                                                                      |  |  |  |  |  |  |  |

|                             | E3950 x7 quad core up to 2.0 GHz                                                                      |  |  |  |  |  |  |  |

|                             | Mechanical                                                                                            |  |  |  |  |  |  |  |

| Dimensions                  | 4.55 x 4.393 in. (115.6 x 111.6 mm)                                                                   |  |  |  |  |  |  |  |

| Weight                      | 4.3 oz. (120 g), without heat sink                                                                    |  |  |  |  |  |  |  |

| PCB thickness               | 0.078 in. (1.98 mm)                                                                                   |  |  |  |  |  |  |  |

|                             | Environmental                                                                                         |  |  |  |  |  |  |  |

| Temperature                 | -40 to +85°C (-40 to +185°F) <sup>a</sup>                                                             |  |  |  |  |  |  |  |

| Humidity (RH)               | 5% to 95% non-condensing                                                                              |  |  |  |  |  |  |  |

| Mechanical shock testing    | MIL-STD-202G, Method 213B, Condition A 50g half-sine,<br>11 ms duration per axis, 3 axis              |  |  |  |  |  |  |  |

| Random vibration testing    | MIL-STD-202G, Method 214A, Condition D .1g/Hz<br>(11.95g rms), 20 minutes per axis, 3 axis            |  |  |  |  |  |  |  |

| Mean time between           | Simulation:                                                                                           |  |  |  |  |  |  |  |

| failure (MTBF) <sup>b</sup> | <ul> <li>Predication standard: Bellcore TR-332, Issue 6 (SR-<br/>332 Issue 1), Electronics</li> </ul> |  |  |  |  |  |  |  |

|                             | Environmental: Temperature 40°C, L1                                                                   |  |  |  |  |  |  |  |

|                             | • Failure rate: 8.876 (FPMH)                                                                          |  |  |  |  |  |  |  |

|                             | • MTBF: 112,664.891 (hrs)                                                                             |  |  |  |  |  |  |  |

| RoHS compliant              | Yes                                                                                                   |  |  |  |  |  |  |  |

| Operating Systems           |                                                                                                       |  |  |  |  |  |  |  |

| Runs 64-bit Windows,        | Linux, and other x86-64-compatible operating systems.                                                 |  |  |  |  |  |  |  |

a. Requires airflow.

b. A MTBF measurement is based on a statistical sample and is not intended to predict any one specific unit's reliability; thus MTBF is not, and should not be construed as, a warranty measurement.

# 7. Configuration

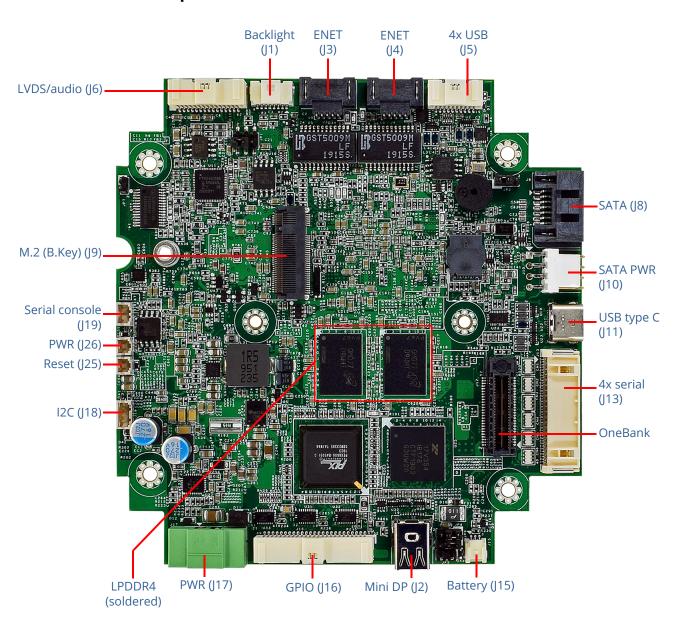

This section describes the PX1-C441 components and configuration.

## 7.1 Component Layout

7.1.1 Top View

#### Top view components

| ltem           | Description                        | Reference |

|----------------|------------------------------------|-----------|

| Power          | 1                                  |           |

| J17            | Power input                        | page 16   |

| J15            | CMOS battery input                 | page 16   |

| J10            | SATA power output                  | page 18   |

| J1             | LVDS backlight power               | page 18   |

| J26            | Power button                       | page 19   |

| J25            | Reset button                       | page 19   |

| Memory and St  | orage                              |           |

|                | LPDDR4 memory                      | page 19   |

|                | eMMC onboard                       | page 19   |

| J9             | M.2 SSD                            | page 19   |

| J8             | SATA 3 (6 Gbps)                    | page 26   |

| Video and Audi | 0                                  |           |

| J2             | Mini DisplayPort++                 | page 20   |

| J6             | LVDS data and HD audio             | page 20   |

| BZ1            | Buzzer speaker                     | page 21   |

| System I/O     |                                    |           |

| J3/J4          | Ethernet 1 and 2                   | page 21   |

| J5             | USB 2.0 ports                      | page 22   |

| J11            | USB 3.2 Gen 1 Type-C               | page 23   |

| J13            | Serial ports 1–4                   | page 23   |

| J19            | Serial RS232 console               | —         |

| J16            | GPIO (general purpose digital I/O) | page 25   |

| J18            | I2C bus                            | —         |

| Jumpers and LE | Ds                                 |           |

| JP1            | LVDS voltage select                | page 27   |

| JP2            | M.2 device type select             | page 27   |

| JP4            | Backlight voltage select           | page 27   |

| JP7            | BIOS reset defaults                | page 27   |

| D3             | System power good/activity LED     | page 28   |

| D7             | PCIe power link                    | page 28   |

| D25            | Ethernet 1 operating at 1000 Mbps  | page 28   |

| D28            | Ethernet 2 operating at 1000 Mbps  | page 28   |

| D26            | Ethernet 1 link activity           | page 28   |

| D27            | Ethernet 2 link activity           | page 28   |

| D34            | Ethernet 1 operating at 100 Mbps   | page 27   |

| D35            | Ethernet 2 operating at 100 Mbps   | page 27   |

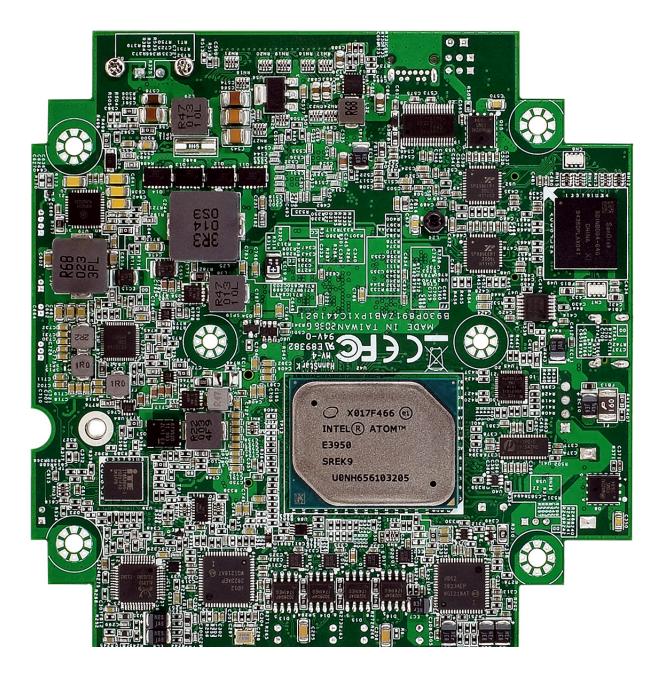

#### 7.1.2 Bottom View

There are no connectors on the bottom of the board.

## 7.2 PCI Devices and Functions

#### **Internal devices**

| Bus | Device | Function | Device ID                                                  | Device/Function Description                 |  |  |

|-----|--------|----------|------------------------------------------------------------|---------------------------------------------|--|--|

| 0   | 0      | 0        | 0F00h                                                      | Device: SoC transaction router              |  |  |

| 0   | 2      | 0        | 0F31h                                                      | Device: Graphics and display                |  |  |

| 0   | 19     | 0        | 0F20h (IDE)<br>0F21h (IDE)<br>0F22h (AHCI)<br>0F23h (AHCI) | Device: SATA                                |  |  |

| 0   | 26     | 0        | 0F18h                                                      | Device: Trusted execution engine            |  |  |

| 0   | 27     | 0        | 0F04h                                                      | Device: HD audio                            |  |  |

| 0   | 0 28 0 |          | 0F48h                                                      | Device: PCI Express*                        |  |  |

|     |        |          |                                                            | Function: Root port 1                       |  |  |

|     |        | 1        | 0F4Ah                                                      | Device: PCI Express*                        |  |  |

|     |        |          |                                                            | Function: Root port 2                       |  |  |

|     |        | 2        | 0F4Ch                                                      | Device: PCI Express*                        |  |  |

|     |        |          |                                                            | Function: Root port 3                       |  |  |

|     |        | 3        | 0F4Eh                                                      | Device: PCI Express*                        |  |  |

|     |        |          |                                                            | Function: Root port 4                       |  |  |

| 0   | 29     | 0        | 0F34h                                                      | Device: EHCI USB                            |  |  |

| 0   | 31     | 0        | 0F1Ch                                                      | Device: Platform controller unit            |  |  |

|     |        |          |                                                            | Function: LPC: Bridge to Intel legacy block |  |  |

| 0   | 31     | 3        | 0F12h                                                      | Device: Platform controller unit            |  |  |

|     |        |          |                                                            | Function: SMBus port                        |  |  |

#### **External devices**

| Bus | Device | Function | Device ID | Device/Function Description         |

|-----|--------|----------|-----------|-------------------------------------|

| 3   | 0      | 0        | 104Ch     | Device: 8240                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 5   | 0      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 6   | 1      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 6   | 2      | 0        | 12D8h     | Device: 2304                        |

|     |        |          |           | Function: PCI/PCI bridge            |

| 7   | 0      | 0        | 8086h     | Device: 8086                        |

|     |        |          |           | Function: Intel Ethernet controller |

| 8   | 0      | 0        | 8086h     | Device: 8086                        |

|     |        |          |           | Function: Intel Ethernet controller |

# 7.3 Watchdog Timer (WDT)

The PX1-C441 features an advanced watchdog timer (WDT) to guard against software lockups; it resets the system if software does not pet the watchdog within the given time-out period. The WDT is implemented in the ITE8528 embedded controller present on the platform. The registers for the WDT can be accessed using the ACPI port 62/66 access mechanism. WINSYSTEMS supports the PX1-C441 WDT in the System Management tools for the PX1-C441. Ask your sales representative for details of this software package.

#### **WDT Registers**

| ACPI Shared RAM Offset<br>of WDT Register | WDT Register Description |

|-------------------------------------------|--------------------------|

| 0x06                                      | WDT CONFIGURATION        |

| 0x07                                      | WDT MINUTES COUNTER      |

| 0x08                                      | WDT SECONDS COUNTER      |

#### 7.3.1 WDT Register Usage

#### Configuration Register (offset 0x06)

| Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0     |

|----------|----------|----------|----------|----------|----------|----------|-----------|

| Not used | WDT mode | WDTenable |

WDT enable WDT mode 0 = disabled, 1 = enabled

0 = seconds mode, 1 = minutes mode

#### Minutes Counter Register (0x07)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSB   |       |       |       |       |       |       | LSB   |

In minutes mode, this register is programmed with the countdown values in minutes. The maximum countdown time when in minutes mode is  $(2^8 - 1 \text{ minutes})$ .

#### Seconds Counter Register (0x08)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSB   |       |       |       |       |       |       | LSB   |

In seconds mode, this register is programmed with the countdown values in seconds. The maximum countdown time when in seconds mode is  $(2^8 - 1 \text{ seconds})$ .

To use the WDT, set the *WDT mode* bit in the configuration register to the desired mode (seconds or minutes), then program the appropriate counter register (minutes or seconds) with the desired countdown value. Then start the WDT by setting the *WDT enable* bit in the configuration register. The WDT begins counting down in the selected mode, and unless the WDT is disabled or reset/pet (see below), the board is reset when the counter register is equal to 0.

To reset or "pet" the watchdog timer, rewrite the minutes or seconds counter register with the countdown value.

To stop the WDT, clear the *WDT enable* bit in the configuration register.

# 7.4 Real-time Clock/Calendar

A real-time clock is used as the AT-compatible clock/calendar. It supports a number of features including periodic and alarm interrupt capabilities. In addition to the time and date-keeping functions, the system configuration is kept in CMOS RAM contained within the clock section. A battery must be enabled for the real-time clock to retain time and date during a power down.

WINSYSTEMS has software available for manipulating the CMOS RTC from a high-level application.

#### 7.5 Connectors

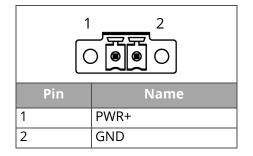

#### 7.5.1 J17 - VIN Power Connector

Use this connection to supply power to the PX1-C441. This computer supports a wide range DC input power from 9 V to 36 V.

#### **Layout and Pin Reference**

#### Connector

Phoenix 1827868 (J17)

#### Matching Connectors

Phoenix 1827703 (housing)

#### 7.5.2 J15 - CMOS Battery Input

An external battery connected to the PX1-C441 provides standby power for the real-time clock (RTC). An extended temperature lithium battery is available from WINSYSTEMS, part number BAT-LTC-E-36-16-2 or BAT-LTC-E-36-27-2. A power supervisory circuit controls an internal power switch to route the battery or standby voltage to the RTC. If power is removed from the system, or the power input voltage drops below the battery voltage, the RTC circuit automatically fails over to battery power.

#### **Layout and Pin Reference**

| Pin | Name                | Description           |

|-----|---------------------|-----------------------|

|     | 1 3                 |                       |

|     | ╔╋═┫                |                       |

|     |                     |                       |

|     | <b>ختکہ سیمکت</b> ن |                       |

| 1   | GND                 | Ground                |

| 2   | VBAT                | Battery input voltage |

| 3   | NC (no connect)     | No connect            |

**WARNING:** BAT-LTC-E-36-16-2 or BAT-LTC-E-36-27-2 must be connected at **J15**. Improper installation of the battery could result in explosive failure. Be careful to note the correct connection at location **J15**.

#### Connector

Molex 501953-0307 1x3, 1 mm pitch (Pico-Clasp<sup>™</sup>) (**J15**)

#### **Matching Connectors**

- Molex 501939-0300 (housing)

- Molex 501334-0100 OR 501334-0000 (crimp)

WINSYSTEMS battery BAT-LTC-E-36-16-2 and BAT-LTC-E-36-27-2 simplify these connections to the board.

#### BAT-LTC-E-36-16-2

BAT-LTC-E-36-27-2

#### 7.5.3 J10 - SATA Power Output

#### **Layout and Pin Reference**

| Pin | Name |  |

|-----|------|--|

|     |      |  |

| 1   | +12V |  |

| 2   | GND  |  |

| 3   | GND  |  |

| 4   | +5V  |  |

#### Connector

Molex 22-12-2044, 1x4 (J10)

#### **Matching Connectors**

- Molex 10-11-2043 (housing)

- Molex 08-55-0124 OR 08-55-0129 (crimp)

#### 7.5.4 J1 - LVDS Backlight Power

#### Layout and Pin Reference

|     | Pin | Name       | Description                  |

|-----|-----|------------|------------------------------|

|     | 1   | +5VDC      | Power                        |

|     | 2   | LBKLT_EN_N | Active low backlight enable  |

|     | 3   | LBKLT_EN_P | Active high backlight enable |

|     | 4   | GND        | Ground                       |

|     | 5   | +12VDC     | +12V backlight power         |

| 1 8 | 6   | PWM        | PWM dimmer signal            |

|     | 7   | NC         | Not connected                |

|     | 8   | NC         | Not connected                |

#### Connector

• Molex 50156-0807, 1x8, 1 mm pitch (Pico-Clasp) (J1)

#### **Matching Connectors**

- Molex 501330-0800 (housing)

- Molex 501334-0000 (crimp)

#### Cable

• CBL-LVDSAB-009-18 (LVDS with analog audio)

add these two sections before LPDDR4 Memory

#### 7.5.5 J26 - Power Button

The PX1-C441 turns on automatically when power is applied to the computer and does not require the power button to be pressed.

The power button connector can be used to wake the computer after shutdown, sleep, or system standby if power is not removed. A momentary switch that shorts the power pin and GND pin together activates the power button input.

This power button also functions with operating system power options, such as safely shutting down the computer or putting the computer to sleep.

Holding the power button for roughly 5 seconds performs a hard reset to the computer.

#### 7.5.6 J25 - Reset Button

The reset button instantly performs a hard reset to the computer.

NOTE To avoid potential operating system corruption, the reset button should only be used when the computer cannot safely shutdown or restart due to a software crash or hardware fault. If the reset button operation is desired, an OS write protect filter is highly recommended.

#### 7.5.7 LPDDR4 Memory

The PX1-C441 provides up to 8 GB of soldered down LPDDR4 system memory (RAM).

#### 7.5.8 eMMC Onboard

The PX1-C441 offers an eMMC solid state disk that provides up to 64 GB of soldered down, onboard storage.

Contact a WINSYSTEMS applications engineer at +1-817-274-7553 for details.

#### 7.5.9 J9 - M.2 Connector (B Key)

The M.2 expansion socket provides support for B key, 2230, and 2242 modules. The M.2, B key interface provides PCIe Gen 2 x2, 1x SATA channel, 1x USB 2.0, and 1x USB 3.2 Gen 1. B key modules typically support M.2 SSDs.

Name

CLK+

GND

GND

AGND

MIC1\_R

MIC1 L

AGND

LINE L

16

18

20

22

24

26

28

30

#### 7.5.10 J8 - SATA 3 (6 Gbps)

The PX1-C441 supports one SATA 3 (6 Gbps) interface.

#### 7.5.11 J2 - Mini DisplayPort++

Standard mini DisplayPort++ (Version 1.2).

NOTE Both Mini DisplayPort and LVDS outputs may be active simultaneously.

#### 7.5.12 J6 - LVDS Data and HD Audio

The PX1-C441 provides one single channel, low voltage differential signaling (LVDS) interface and backlight power (see "J1 - LVDS Backlight Power" on page 18).

The LVDS panel voltage (SWVDD) is user selectable via jumper **JP1**. Voltage options available are 3.3 V, 5 V, and 12 V (see "JP1 - LVDS Voltage Select" on page 27).

NOTE Both LVDS and Mini DisplayPort outputs may be active simultaneously.

CLK-

GND

OUT R

OUT L

AGND

LINE R

DDC\_CLK

DDC DATA

|  | Pin | Name  | Pin |     |

|--|-----|-------|-----|-----|

|  | 1   | SWVDD | 2   | GND |

|  | 3   | D0-   | 4   | D0+ |

|  | 5   | D1-   | 6   | D1+ |

|  | 7   | SWVDD | 8   | GND |

|  | 9   | D2-   | 10  | D2+ |

|  | 11  | D3-   | 12  | D3+ |

|  | 13  | SWVDD | 14  | GND |

|  |     |       |     |     |

15

17

19

21

23

25

27

29

#### Layout and Pin Reference

#### **Additional Information**

WINSYSTEMS offers these cables for the LVDS interface:

- CBL-LVDSAB-009-18 (LVDS with analog audio)

- CBL-SPL-001-14 (analog audio, unterminated LVDS lines)

#### Connector

Molex 501571-3007, 2x15, 1 mm pitch (Pico-Clasp) (J6)

#### **Matching Connector**

- Molex 501189-3010 (housing)

- Molex 501193-2000 (crimp)

#### 7.5.13 BZ1 - Buzzer Speaker

An onboard speaker, BZ1, is available for sound generation. The BIOS activates the buzzer during POST. In case of POST failure, each error has its own unique beep code. Refer to "BIOS Status and Errors" for details.

#### 7.5.14 J3 and J4 - LAN Ethernet Ports

#### **Layout and Pin Reference**

| J3/J4 | Pin | 100Base-T | 1000Base-T |

|-------|-----|-----------|------------|

|       | 1   | TX+       | BI_DA+     |

| 2 10  | 2   | TX-       | BI_DA-     |

|       | 3   | RX+       | BI_DB+     |

|       | 4   |           | BI_DC+     |

|       | 5   |           | BI_DC-     |

| 1 9   | 6   | RX-       | BI_DB-     |

|       | 7   |           | BI_DD+     |

|       | 8   |           | BI_DD-     |

|       | 9   | GND       | GND        |

|       | 10  | GND       | GND        |

#### **Additional Information**

The PX1-C441 is equipped with two Intel i210 Gigabit Ethernet controllers. Each controller provides a standard IEEE 802.3 Ethernet interface for 1000/100/10BASE-T networks. The connections for each Ethernet port are available at **J3** and **J4**.

Onboard Ethernet activity LEDs D26, D25, and D24 provide status for Port 1. LEDs D27, D28, and D35 provide status for Port 2. These LEDs indicate operation at 1 Gbps, link activity, and operation at 100 Mbps. (See "LED Indicators D3 - D35" on page 28.)

WINSYSTEMS offers the cable CBL-ENET1-302-12 to simplify this connection. This cable interfaces with one Ethernet connection only. A second cable is required for dual Ethernet operation.

#### Connector

Samtec TFM-105-02-L-DH (J3 and J4)

#### **Mating Connector**

- Samtec ISDF-05-D-M (housing)

- CC03L-2830-01-G or CC03R-2830-01-G (crimp)

#### 7.5.15 J5 - USB 2.0 Ports

The PX1-C441 supports four USB 2.0 ports through one onboard connector. They feature ESD suppression, as well as short circuit and overload protection.

#### **Layout and Pin Reference**

| Pin      | Name     | Pin | Name     |  |  |  |

|----------|----------|-----|----------|--|--|--|

| USB (J5) | USB (J5) |     |          |  |  |  |

|          | 19       | _1  |          |  |  |  |

|          |          |     |          |  |  |  |

|          | 20       | 2   |          |  |  |  |

| 1        | USB0_PWR | 2   | USB1_PWR |  |  |  |

| 3        | USB0-    | 4   | USB1-    |  |  |  |

| 5        | USB0+    | 6   | USB1+    |  |  |  |

| 7        | USB_GND  | 8   | USB_GND  |  |  |  |

| 9        | USB_GND  | 10  | USB_GND  |  |  |  |

| 11       | USB_GND  | 12  | USB_GND  |  |  |  |

| 13       | USB2_PWR | 14  | USB3_PWR |  |  |  |

| 15       | USB2-    | 16  | USB3-    |  |  |  |

| 17       | USB2+    | 18  | USB3+    |  |  |  |

| 19       | USB_GND  | 20  | USB_GND  |  |  |  |

#### Connector

Molex 501571-2007, 2x10, 1 mm pitch (Pico-Clasp) (J5)

#### **Matching Connectors**

- Molex 501189-2010 (housing)

- Molex 501193-2000 (crimp)

The USB cable terminates to the 20-pin connector at **J5**. Use WINSYSTEMS cable CBL-USB4-000-14, CBL-USB4-001-12, or CBL-USB4-002-12, along with ADP-IO-USB-001.

v1.01

#### 7.5.16 J11 - USB 3.2 Gen 1 Type-C

One USB 3.2 Gen 1 (5 Gbps) port is supported with a Type-C onboard connector.

#### 7.5.17 J13 - Serial Ports 1–4

#### Serial Ports 1–4 RS232/RS422/RS485 Connectors

The PX1-C441 provides four 16550-compatible serial ports through COM A to COM D. COM C and COM D support RS232, RS422, and RS485 modes. COM A and COM B are RS232 only. Mode selection (RS232/RS422 or RS485 half duplex/full duplex) is selectable in the BIOS. All other capabilities are enabled/disabled through the provided device driver.

# Layout and Pin Reference

|               | Pin | Name     | Pin | Name     |

|---------------|-----|----------|-----|----------|

|               | 1   | COM1_DCD | 2   | COM1_DSR |

|               | 3   | COM1_RX  | 4   | COM1_RTS |

|               | 5   | COM1_TX  | 6   | COM1_CTS |

|               | 7   | COM1_DTR | 8   | COM1_RI  |

|               | 9   | GND      | 10  | NC       |

|               | 11  | COM2_DCD | 12  | COM2_DSR |

|               | 13  | COM2_RX  | 14  | COM2_RTS |

|               | 15  | COM2_TX  | 16  | COM2_CTS |

|               | 17  | COM2_DTR | 18  | COM2_RI  |

| 39 [1] 集幕] 40 | 19  | GND      | 20  | NC       |

|               | 21  | COM3_DCD | 22  | COM3_DSR |

|               | 23  | COM3_RX  | 24  | COM3_RTS |

|               | 25  | COM3_TX  | 26  | COM3_CTS |

|               | 27  | COM3_DTR | 28  | COM3_RI  |

|               | 29  | GND      | 30  | NC       |

|               | 31  | COM4_DCD | 32  | COM4_DSR |

|               | 33  | COM4_RX  | 34  | COM4_RTS |

|               | 35  | COM4_TX  | 36  | COM4_CTS |

|               | 37  | COM4_DTR | 38  | COM4_RI  |

|               | 39  | GND      | 40  | NC       |

#### Serial Ports 1–4 DB9 Male Connector

#### Layout and Pin Reference

| Pin | RS232 | RS422 | RS485  |

|-----|-------|-------|--------|

| 1   | DCD   | NA    | NA     |

| 2   | RX    | TX+   | TX/RX+ |

| 3   | TX    | TX-   | TX/RX  |

| 4   | DTR   | NA    | NA     |

| 5   | GND   | GND   | GND    |

| 6   | DSR   | RX+   | NA     |

| 7   | RTS   | RX_   | NA     |

| 8   | CTR   | NA    | NA     |

| 9   | RI    | NA    | NA     |

All ports are configured as data terminal equipment (DTE). Both the send and receive registers of each port have a 16-byte FIFO. All serial ports have 16C550-compatible UARTs. The RS232 has a charge pump to generate the plus and minus voltages so the PX1-C441 only requires +5 V to operate. An independent, software-programmable baud rate generator is selectable from 300 through 921.6 kbps. Individual modem handshake control signals are supported for all ports.

WINSYSTEMS cables simplify connections to the board:

- CBL-SER4-000-14: Duo-Clasp<sup>™</sup> to unterminated

- CBL-SER4-001-12: Duo-Clasp to Duo-Clasp

- CBL-SER4-002-12: Duo-Clasp to 4xDB9

#### Connector

• Molex 502046-4070, 2x20, 1.25 mm pitch (Duo-Clasp) (**J13**)

#### **Matching Connectors**

- Molex 503110-4000 (housing)

- Molex 501930-1100 (crimp)

#### 7.5.18 J16 - GPIO24 General-Purpose Input/Output

The PX1-C441 supplies 24, 5 V-tolerant GPIO lines with rising/falling edge event sense interrupt generation.

#### **Layout and Pin Reference**

|                | Pin | Name      | Pin | Name |

|----------------|-----|-----------|-----|------|

|                | 1   | GPIO1_C7  | 2   | GND  |

|                | 3   | GPIO2_C6  | 4   | GND  |

|                | 5   | GPIO3_C5  | 6   | GND  |

|                | 7   | GPIO4_C4  | 8   | GND  |

|                | 9   | GPIO5_C3  | 10  | GND  |

| 1 (= = = 2     | 11  | GPIO6_C2  | 12  | GND  |

|                | 13  | GPIO7_C1  | 14  | GND  |

|                | 15  | GPIO8_C0  | 16  | GND  |

|                | 17  | GPIO9_B7  | 18  | GND  |

|                | 19  | GPIO10_B6 | 20  | GND  |

|                | 21  | GPIO11_B5 | 22  | GND  |

|                | 23  | GPIO12_B4 | 24  | GND  |

|                | 25  | GPIO13_B3 | 26  | GND  |

| 49 [======= 50 | 27  | GPIO14_B2 | 28  | GND  |

|                | 29  | GPIO15_B1 | 30  | GND  |

|                | 31  | GPIO16_B0 | 32  | GND  |

|                | 33  | GPIO17_A7 | 34  | GND  |

|                | 35  | GPIO18_A6 | 36  | GND  |

|                | 37  | GPIO19_A5 | 38  | GND  |

|                | 39  | GPIO20_A4 | 40  | GND  |

|                | 41  | GPIO21_A3 | 42  | GND  |

|                | 43  | GPIO22_A2 | 44  | GND  |

|                | 45  | GPIO23_A1 | 46  | GND  |

|                | 47  | GPIO24_A0 | 48  | GND  |

|                | 49  | +5V       | 50  | GND  |

#### Connector

- Molex 501571-5007 2x25, 1 mm pitch (Pico-Clasp) (J16)

- (WS G650-2050-7HB)

#### Cables

- CBL-DIO24-001-12: Pico-Clasp to Pico-Clasp

- CBL-DIO24-002-12: Pico-Clasp to 2x25, 0.1" pitch housing

### 7.5.19 J12 - PCle OneBank

#### Layout and Pin Reference

| Pin | Name       | Pin | Name       |

|-----|------------|-----|------------|

| 1   | USB_OC#    | 2   | PE_RST#    |

| 3   | 3.3V_1     | 4   | 3.3V_2     |

| 5   | USB_1P     | 6   | USB_0P     |

| 7   | USB_1N     | 8   | USB_0N     |

| 9   | GND1       | 10  | GND2       |

| 11  | PEx1_1TP   | 12  | PEx1_0TP   |

| 13  | PEx1_1TN   | 14  | PEx1_0TN   |

| 15  | GND3       | 16  | GND4       |

| 17  | PEx1_2TP   | 18  | PEx1_3TP   |

| 19  | PEx1_2TN   | 20  | PEx1_3TN   |

| 21  | GND5       | 22  | GND6       |

| 23  | PEx1_1RP   | 24  | PEx1_0RP   |

| 25  | PEx1_1RN   | 26  | PEx1_0RN   |

| 27  | GND7       | 28  | GND8       |

| 29  | PEx1_2RP   | 30  | PEx1_3RP   |

| 31  | PEx1_2RN   | 32  | PEx1_3RN   |

| 33  | GND9       | 34  | GND10      |

| 35  | PEx1_1CLKP | 36  | PEx1_0CLKP |

| 37  | PEx1_1CLKN | 38  | PEx1_0CLKN |

| 39  | +5V_SB_1   | 40  | +5V_SB_2   |

| 41  | PEx1_2CLKP | 42  | PEx1_3CLKP |

| 43  | PEx1_2CLKN | 44  | PEx1_3CLKN |

| 45  | DIR        | 46  | PWRGOOD    |

| 47  | SMB_DAT    | 48  | NC         |

| 49  | SMB_CLK    | 50  | NC         |

| 51  | SMB_ALERT  | 52  | PSON#      |

#### 7.6 Jumpers

NOTE Jumper part number SAMTEC 2SN-BK-G applies to all jumpers. These are available in ten-piece kits from WINSYSTEMS. Order part number KIT-JMP-G-200.

#### 7.6.1 JP1 - LVDS Voltage Select

#### **Layout and Pin Reference**

|       | Selection | Jumper Positions             |

|-------|-----------|------------------------------|

| 2 4 6 | 3.3V      | Jumper pins 1 and 3 together |

|       | 5V        | Jumper pins 3 and 5 together |

|       | 12V       | Jumper pins 3 and 4 together |

#### 7.6.2 JP2 - M.2 Device Type Select

Select either MiniPCIe or mSATA at socket **J9**.

#### **Layout and Pin Reference**

|                   | Selection | Jumper Positions             |

|-------------------|-----------|------------------------------|

|                   | mSATA     | Jumper pins 1 and 2 together |

| 3 □<br>2 □<br>1 ■ | mPCle     | Jumper pins 2 and 3 together |

#### 7.6.3 JP4 - Backlight Voltage Select

Select either 5 or 12 V for backlight voltage level.

#### **Layout and Pin Reference**

|                   | Selection             | Jumper Positions             |

|-------------------|-----------------------|------------------------------|

|                   | Backlight voltage 5V  | Jumper pins 1 and 2 together |

| 3 □<br>2 □<br>1 🖬 | Backlight voltage 12V | Jumper pins 2 and 3 together |

#### 7.6.4 JP7 - CMOS Clear

A jumper provided onboard enables you to reset the BIOS CMOS settings to factory defaults. The BIOS reads this pin during system boot and forces the settings to reset if the pin is at ground.

To reset the BIOS CMOS parameters, place jumper **JP7** in the **Clear CMOS entries** mode, apply power to the board, and let it boot into the BIOS. Power off the board, and restore **JP7** to the **Normal operation** position.

#### **Layout and Pin Reference**

|                   | Selection          | Jumper Positions             |

|-------------------|--------------------|------------------------------|

|                   | Normal operation   | Jumper pins 1 and 2 together |

| 3 □<br>2 □<br>1 ■ | Clear CMOS entries | Jumper pins 2 and 3 together |

#### 7.7 LED Indicators D3 - D35

The activity LED is on the Atom E3900 GPIO\_27 and can be accessed at address 0xD0C505D8. Setting the GPIO pin high turns on the LED, setting it low turns off the LED.

#### **LED Reference**

| LED | Description          | Color |

|-----|----------------------|-------|

| D3  | System power good    |       |

| D7  | PCIe power link      | Green |

| D25 | Ethernet 1 1000 Mbps | Amber |

| D26 | Ethernet 1 Link      | Green |

| D27 | Ethernet 2 Link      | Green |

| D28 | Ethernet 2 1000 Mbps | Amber |

| D34 | Ethernet 1 100 Mbps  | Green |

| D35 | Ethernet 2 100 Mbps  | Green |

# 8. **BIOS Functionality**

The BIOS used in this design is a custom version of the AMI Aptio V x86 BIOS.

### 8.1 References

The following Intel Atom E3900 BIOS specification documents can assist developers in the creation of firmware for the Intel Atom E3900:

- Intel Atom E3900 Platform Intel Architecture Firmware Specification (Volume 1 of 2), Document Number 559810

- Intel Atom E3900 Platform Intel Architecture Firmware Specification (Volume 2 of 2), Document Number 559811

- Intel Dynamic Platform and Thermal Framework (Intel DPTF) v8.x 201 -Rev 1.1, Document Number 556073

#### 8.2 Glossary

- advanced configuration and power interface (ACPI): Specification that establishes industry standard interfaces enabling OS directed configuration, power management and thermal management of mobile, desktop, and server platforms.

- dynamic video memory technology (DVMT): Allows dynamic allocation of system memory for use as video memory to ensure the most efficient use of available resources in order to maximize 2D/3D graphics performance.

- graphics processing unit (GPU): Specialized electronic circuit designed to rapidly manipulate and alter memory to accelerate the creation of images in a frame buffer.

- integrated graphics device (IGD): Graphics processor integrated into the Intel Atom E3900 SOC. The IGD in the Atom E3900 SOC is an Intel 9th Generation GPU, also called Gen9 GPU.

- Unified Extensible Firmware Interface (UEFI): Specification that defines a software interface between an operating system and platform firmware. UEFI replaces the basic input/output system (BIOS) firmware interface

#### 8.3 BIOS Settings

This section provides details on the system parameters that are managed by the BIOS. If a BIOS parameter can be changed, details on the possible parameter values are included.

#### 8.3.1 Main

The Main page of the BIOS displays general information related to the current BIOS build, including the BIOS and embedded controller firmware revisions, the revision of built in SOC device firmware, and CPU-specific values (processor stepping and name).

The Main BIOS page also contains information related to the amount and configuration of the system RAM (the type of RAM used in the design).

The following BIOS build information is available on the Main BIOS page.

| Project Name:                         | PX1-C441                              |

|---------------------------------------|---------------------------------------|

| BIOS Version & Build Date:            | 71215T00 (12/15/2017 18:18:05)        |

| EC Version & Build Date:              | 70605T01 (06/05/2017)                 |

| Access Level:                         | Administrator                         |

| Processor information Brand<br>String | Intel Atom Processor E39X0 @ 1.30 GHz |

Platform Firmware Information

| BXT SOC            | B1                                |

|--------------------|-----------------------------------|

| TXE FW             | 3.1.50.2222                       |

| GOP                | 10.0.1035                         |

| CPU Flavor         | BXT Notebook/Desktop <sup>a</sup> |

| Memory Information |                                   |

| Total Memory       | 8192 MB                           |

| Memory Slot 0      | 8192 (DDR3L ECC)                  |

| Memory Speed       | 1600 MHz                          |

| System Date        | [Mon 03/27/2017]                  |

| System Time        | [09:51:15]                        |

a. The CPU Flavor field reflects the actual Atom E3900 processor installed on the PX1-C441 platform. In this case, it indicates that the processor is an industrial Intel Atom E39x0 processor, but it could also indicate the processor is a Celeron N3350 @ 1.10 GHz, or a Pentium N4200 @ 1.10 GHz.

#### 8.3.2 Configuration

The BIOS Configuration page serves as the top-level BIOS page for configuring peripherals and devices present on the PX1-C441 platform. The configuration sub-pages include but are not limited to pages for the CPU, network interfaces, serial ports, USB ports, and SATA. The settings for each configuration sub-page are described in the device sections.

#### **CPU** Configuration

The configuration values related to the CPU cores, CPU cache, CPU patch level, and integrated CPU capability are detailed on this BIOS page.

| CPU signature                                             | 506C9                  |

|-----------------------------------------------------------|------------------------|

| Microcode patch level                                     | 20                     |

| Max CPU speed                                             | 1300 MHz               |

| Min CPU speed                                             | 800 MHz                |

| Processor cores <sup>a</sup>                              | 2                      |

| Intel HT Technology <sup>b</sup>                          | Not supported          |

|                                                           |                        |

| Intel VT-x Technology <sup>c</sup>                        | Supported              |

| Intel VT-x Technology <sup>c</sup><br>64-bit <sup>d</sup> | Supported<br>Supported |

|                                                           |                        |

| 64-bit <sup>d</sup>                                       | Supported              |

| 64-bit <sup>d</sup><br>L1 data cache                      | Supported<br>24 kB x 2 |

| Active Processor Cores <sup>e</sup>          | [Disabled/enabled] |

|----------------------------------------------|--------------------|

| Core 0 <sup>f</sup>                          | [Enabled/disabled] |

| Core 1 <sup>g h</sup>                        | [Enabled/disabled] |

| Intel Virtualization Technology <sup>i</sup> | [Enabled/disabled] |

| VT-d <sup>j</sup>                            | [Enabled/disabled] |

| CPU power management configuration           |                    |

| EIST <sup>k</sup>                            | [Enabled/disabled] |

| Turbo Mode                                   | [Enabled/disabled] |

| C-States                                     | [Enabled/disabled] |

| Enhanced C-states                            | [Enabled/disabled] |

- a. The PX1-C441 used to help define the BIOS requirements contained an E3930 dual-core SOC. The PX1-C441 board also supports the use of the E3940 and E3950 quad-core SOCs.

- b. Intel Hyper Threading technology a proprietary technology that enhances the CPU's multi-threading capability to allow parallelization of computations. HTT is not implemented in the Intel Atom E3900 SOC.

- c. VT-x is Intel's proprietary processor virtualization technology.

- d. 64-bit technology is the ability of the CPU to execute 64 bit instructions.

- e. Allows individual processor cores to be enabled or disabled.

- f. Core 0 is not visible if Active Processor Cores is disabled.

- g. Core 1 is not visible if Active Processor Cores is disabled.

- h. If the board is populated with an E3940 or E3950 SOC, this list includes Core 2 and Core 3 devices.

- i. If the CPU contains the Intel VT-x technology, then this field can be used to enable/disable the built-in virtualization capabilities.

- j. VT-d is the ability of the SOC to allow direct access to built-in peripherals by running virtual machines. It is sometimes referred to as IO MMU virtualization.

- k. EIST is also known as SpeedStep technology. This technology allows the clock speed of the processor to be dynamically modified by software.

#### **Memory Configuration**

| ECC Error Rate Injection                    | No Error                       |

|---------------------------------------------|--------------------------------|

| Refresh Rate of 2x <sup>a</sup>             | Enable                         |

| a. Ensures that refresh rate never drops be | elow 2x. Enable:2x Disable:1x. |

# Chipset Configuration

| High Precision Timer           | [Enable/disable] |

|--------------------------------|------------------|

| HD-Audio Support               | [Enable/disable] |

| 8254 Clock Gating <sup>a</sup> | [Enable/disable] |

a. 8254 clock gating allows shutdown of the crystal. It is used for maximum power saving.

#### **LAN Configuration**

The LAN configuration page displays the MAC addresses for the built-in Ethernet NICs, and allows network features to be enabled or disabled. Features that can be enabled in the BIOS include Wake On LAN and PXE network boot.

| Wake On LAN <sup>a</sup>                              | [Enable/disable]   |

|-------------------------------------------------------|--------------------|

| Intel Ethernet Controller WGI210AT<br>LAN MAC Address | XX:XX:XX:XX:XX:XX  |

| Intel Ethernet Controller WGI210AT<br>LAN MAC Address | XX:XX:XX:XX:XX:XX  |

| Launch UEFI RXE Rom                                   | [Enabled/disabled] |

| PXE ROM <sup>b</sup>                                  |                    |

| IPv4 PXE Support                                      | [Enabled/disabled] |

| IPv6 PXE Support                                      | [Enabled/disabled] |

- a. Wake On LAN is a feature that allows a computer to be awoken or powered on when a wake packet is detected on the network interface.

- b. PXE boot is a BIOS feature that allows a computer to boot its operating system and root file system across a network. It is useful when implementing diskless workstation.

#### **Graphics Configuration**

The graphics configuration page of the BIOS allows the user to specify settings used by the Intel Gen9 GPU.

| DVMT Pre-Allocated <sup>a</sup>                                                                | [64M/96M/128M/160M/192M/224M/256M/<br>288M/320M/352M/384M/416M/448M/480M/<br>512M] |  |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| IGD Output Display Contr                                                                       | ol - GOP                                                                           |  |

| GOP driver                                                                                     | [Enable/Disable]                                                                   |  |

| IGD Output Display Control - CSM <sup>b</sup>                                                  |                                                                                    |  |

| Primary IGFX Boot<br>Display                                                                   | [AUTO, EFP, LFP, EFP2]                                                             |  |

| Secondary IGFX Boot<br>Display <sup>c</sup>                                                    | [Disabled,EFP,LFP,EFP2]                                                            |  |

| a. The DVMT RAM amount selects the pre-allocated (fixed) graphics memory size used by the IGD. |                                                                                    |  |

- b. These settings select the video device that is activated during the POST.

- c. The Secondary IGFX Boot Display selection is not enabled unless the Primary IGFX Boot Display is set to some value other than AUTO. If the Primary IGFX Boot Display is set to EFP, LFP, or EFP2, then the Secondary IGFX Boot Display settings become visible, and can be set to one of the built in values (EFP, LP, EFP2).

#### eDP-to-LVDS Configuration

The parameters under this configuration page define how the embedded DisplayPort is mapped to the LVDS display interface, and permit the user to set the LVDS panel profile.

| Panel Profile <sup>a</sup>                                       | [640x480,800x480,800x600,1024x768,1280x800,1280<br>x1024,1366x768,1440x900,1920x1080, OEM Profile] |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| Color Depth and<br>data format <sup>b</sup>                      | [VESA 24BPP, JEIDA 24BPP, VESA and JEIDA 18BPP]                                                    |  |

| Channel Mode                                                     | [Single Channel, Dual Channel]                                                                     |  |

| Clock Mode                                                       | [Even Bus, Odd Bus, Both Buses]                                                                    |  |

| OEM Profile <sup>c</sup>                                         |                                                                                                    |  |

| Profile Name                                                     |                                                                                                    |  |

| Color Depth<br>and data                                          |                                                                                                    |  |

| Channel Mode                                                     |                                                                                                    |  |

| Pixel Clock                                                      |                                                                                                    |  |

| H Active Pixels                                                  |                                                                                                    |  |

| H Blank Pixels                                                   |                                                                                                    |  |

| H Offset Pixels                                                  |                                                                                                    |  |

| H Width Pixels                                                   |                                                                                                    |  |

| V Active Lines                                                   |                                                                                                    |  |

| V Blank Lines                                                    |                                                                                                    |  |

| V Offset Lines                                                   |                                                                                                    |  |

| V Width Lines                                                    |                                                                                                    |  |

| H & V sync<br>Signal Polarity                                    | [Positive, Non-Positive]                                                                           |  |

| a. Specifies the geometry and mode of the attached LVDS display. |                                                                                                    |  |

- b. Allows the bits per pixel and pixel data format to be specified.

- c. The OEM profile allows a user to define a non-standard LVDS display profile.

#### **PCI/PCIe Configuration**

This section allows the user to set the PCI, PCI-X and PCI-express parameters.

| PCI Express Root Port 1 - 6 |                  |

|-----------------------------|------------------|

| PCI Express Root Port #     | [Enable/disable] |

| ASPM <sup>a</sup>           | [Enable/disable] |

| Hot Plug                    | [Enable/disable] |

PCIe Speed

[Auto/Gen1/Gen2/Gen3]

PCIe Selectable De-emphasis

[Enable/disable]

PCle Port configuration table <sup>b</sup>

- a. Active State Power Management A power conservation protocol used with PCI serial devices that places the device into a low power mode as the device becomes less active over time.

- b. Displays PCIe port configuration, link width, and link speed for any PCIe device present

#### **SATA Configuration**

The SATA configuration page is used to configure and enable the PX1-C441's SATA functionality.

| SATA Controller <sup>a</sup>       | [Enable/Disable]                    |  |

|------------------------------------|-------------------------------------|--|

| SATA Speed Selection <sup>b</sup>  | [Auto/Gen1/Gen2/Gen3]               |  |

| SATA Port 0                        | {Installed device name}             |  |

| Port 0                             | [Enable/Disable]                    |  |

| SATA Port 0 Hot Plug<br>Capability | [Enable/Disable]                    |  |

| SATA Device Type                   | [Hard Disk Drive/Solid State Drive] |  |

| SATA Port 1                        | {Installed device name}             |  |

| Port 1                             | [Enable/Disable]                    |  |

| SATA Port 1 Hot Plug<br>Capability | [Enable/Disable]                    |  |

| SATA Device Type                   | [Hard Disk Drive/Solid State Drive] |  |

- a. Enables or disables the built in SATA controller.

- b. Selects the SATA interface speed. SATA Gen1 speed is 1.5 Gbits/second, Gen2 is 3.0 Gbits/second, and Gen3 is 6.0 Gbits/second.

#### **USB** Configuration

This set of BIOS parameters specifies the setup and configuration of the USB interfaces present on the PX1-C441 board.

| USB Controller                                      |                  |

|-----------------------------------------------------|------------------|

| 1 XHCI                                              |                  |

| USB Devices                                         |                  |

| 1 Drive, 1 Keyboard, 1<br>Mouse, 1 Hub <sup>a</sup> |                  |

| SOC USB Configuration                               |                  |

| USB Port #0                                         | [Enable/Disable] |

| USB Port #1                                         | [Enable/Disable] |

|                                                     |                  |

| USB Port #2                                      | [Enable/Disable]          |  |

|--------------------------------------------------|---------------------------|--|

| USB Port #3                                      | [Enable/Disable]          |  |

| USB Port #4                                      | [Enable/Disable]          |  |

| USB Port #5                                      | [Enable/Disable]          |  |

| USB Port #6                                      | [Enable/Disable]          |  |

| USB Port #7                                      | [Enable/Disable]          |  |

| Common USB Configuration                         |                           |  |

| Legacy USB Support <sup>b</sup>                  | [Enable/Disable]          |  |

| USB Mass Storage Driver<br>Support               | [Enable/Disable]          |  |

| USB hardware delays and time-<br>outs            |                           |  |

| USB Transfer time-out                            | [1/5/10/20 seconds]       |  |

| Device reset time-out                            | [10/20/30/40 seconds]     |  |

| Device power-up delay                            | [Auto/Manual]             |  |

| Device power-up delay in<br>seconds <sup>c</sup> | [140 seconds]             |  |

| Mass Storage Devices <sup>d</sup>                |                           |  |

| SanDisk                                          | [Auto/Floppy/Forced FDD/H |  |

[Auto/Floppy/Forced FDD/Hard Disk/ CD-ROM]

- a. Contents of this line depend upon the devices connected to the USB ports at boot time.

- b. Legacy USB support and USB mass storage driver support are used with the Compatibility System Module to support the booting of legacy (non-UE-Fl) operating systems.

- c. This field only appears when **Device power-up delay** is set to **Manual**.

- d. Devices displayed below this line depend on the devices plugged into USB ports at the time the system booted.

#### **Power Control Configuration**

| Enable Hibernation <sup>a</sup>    | [Enable/Disable]                       |  |

|------------------------------------|----------------------------------------|--|

| ACPI Sleep State <sup>b</sup>      | [Suspend disabled/S3 (Suspend to RAM)] |  |

| Restore AC Power Loss <sup>c</sup> | [Power On/Power Off/Last State]        |  |

| RTC Wakeup <sup>d</sup>            | [Enabled/disabled]                     |  |

| System Time                        | [HH:MM:SS]                             |  |

| Wake up day <sup>e</sup>           | 031                                    |  |

| Wake up Time                       | [HH:MM:SS]                             |  |

- a. Allows the system ability to hibernate (S4) to be enabled or disabled.

- b. Selects the highest ACPI sleep state the system enters when the **SUSPEND** button is pressed.

- c. Specifies the state the system enters when power is reapplied after a power failure. If set to **POWER ON**, the system boots as soon as power is enabled. If set to **POWER OFF**, the system remains powered off until the power button is pressed.

- d. Enables or disables the system wake on alarm event. If this setting is **enabled**, the BIOS allows the user to set the **Wake up day** and **Wake up Time** fields below.

- e. Day of the month.

#### **Thermal Configuration**

#### **Thermal Configuration Parameters**

Automatic Thermal Reporting <sup>a</sup> [Enabled/Disabled]

a. When enabled, Automatic Thermal Reporting automatically configures the CRITICAL, PASSIVE, and ACTIVE trip points based on recommended values.

#### **Dynamic Platform and Thermal Framework**

The dynamic platform and thermal framework (DPTF) is a platform-level software framework that serves as a base for any power, thermal, or other platform-level control technology. DPTF uses advanced configuration and power interface (ACPI) as the primary interface to communicate with the platform and to gather policy inputs and preferences for each technology. The ACPI specification was developed to establish industry common interfaces enabling robust operating system (OSPM) directed motherboard device configuration and power management.

The DPTF allows thermal points to be set for various participants. When the trip points are reached, the DPTF configuration specifies what actions are initiated to address the thermal and power conditions. Actions range from turning on active cooling devices (i.e., a fan), to down clocking the CPU.

| DPTF                                     |                                          | [Enable/Disable]       |

|------------------------------------------|------------------------------------------|------------------------|

| DPTF Configuration                       |                                          | [six bit bitmap value] |

| BIT 0                                    | Generic UI Access Control                | [0=enable/1=disable]   |

| BIT 1                                    | Restricted UI Access Control             | [0=enable/1=disable]   |

| BIT 2                                    | Shell Access Control                     | [0=enable/1=disable]   |

| BIT 3                                    | Environment Monitoring<br>Report Control | [0=enable/1=disable]   |

| BIT 4                                    | Thermal Mitigation Report<br>Control     | [0=enable/1=disable]   |

| BIT 5                                    | Thermal Policy Report Control            | [0=enable/1=disable]   |

| DPTF Processor                           |                                          | [Enable/Disable]       |

| Active Thermal Trip Point <sup>a b</sup> |                                          | 90                     |

| Passive Thermal Trip Point <sup>a</sup>  |     |

|------------------------------------------|-----|

| S3/CS Thermal Trip Point <sup>a</sup>    | 110 |

| Hot Thermal Trip Point <sup>a</sup>      | 110 |

| Critical Thermal Trip Point <sup>a</sup> | 105 |

| Thermal Sampling Period <sup>c</sup>     | 0   |

| S3/CS Thermal Trip Point <sup>a</sup>    | 110 |

| Hot Thermal Trip Point <sup>a</sup>      | 110 |

| Critical Thermal Trip Point <sup>a</sup> | 105 |

| Thermal Sampling Period <sup>c</sup>     | 0   |

a. Temperature, in Celsius; a value of 0 disables trip point.

b. If DPTF processor is **Disabled**, these fields are no visible.

c. Polling Interval in 1/10 seconds; a value of 0 enables interrupts

#### **Serial Port Configuration**

| COM1 Mode | [RS232/RS485 HALF DUPLEX/RS485.422 FULL DUPLEX] |

|-----------|-------------------------------------------------|

| COM2 Mode | [RS232/RS485 HALF DUPLEX/RS485.422 FULL DUPLEX] |

The built-in serial ports may be configured using the Serial Port Configuration page of the BIOS.

Serial ports A and B are RS232 only ports. Serial ports C and D may be configured as RS232, RS422, or RS485 devices. The BIOS serial port settings support the simultaneous transmission and reception of data on the discrete RX and TX lines (full-duplex), or the shared transmission and reception of data on a single data line pair (half-duplex).

Additional serial port configuration is performed using the Windows Device Manager and the EXAR Quad UART device driver.

Watch Dog Timer Configuration

| Watch Dog Timer | [Enabled/Disabled] |

|-----------------|--------------------|

| Timer Unit      | [Second/Minute]    |

| Timer Value     | Ν                  |

The PX1-C441's watchdog timer can be enabled or disabled using the BIOS. When enabled, the WDT timer unit value may be specified as either seconds or minutes. The watchdog timer value N can also be set on this BIOS page.

If the watchdog timer is disabled on this page, the Timer Unit and Timer Value fields are disabled.

#### **H/W Monitor**

The BIOS supports monitoring of CPU temperature, CPU voltages, and system voltages. The currently measured values may be displayed using the H/W Monitor BIOS page. The H/W Monitor page displays the following values.

| CPU Temperature | Current Temperature (in Celsius) |

|-----------------|----------------------------------|

| Fan1 Speed      |                                  |

| Vcore           | Current detected voltage         |

| +3.3V           | Current detected voltage         |

| +5V             | Current detected voltage         |

| +12V            | Current detected voltage         |

| VDIMM           | Current detected voltage         |

#### **Debug Configuration**

The Debug Configuration page enables or disables the built in DCI-USB debug interface.

DCI Enable (HDCIEN) [Enabled/Disabled]

#### Intel I210 Gigabit Network Connection - XX:XX:XX:XX:XX:XX:XX

| NIC Configuration   |                                       |

|---------------------|---------------------------------------|

| Blink LEDs          | [0/1]                                 |

| UEFI Driver         | Intel PRO/1000 7.3.20 PCI-E           |

| Adapter PBA         | 000300-000                            |

| Device Name         | Intel I210 Gigabit Network Connection |

| Chip Type           | Intel i210                            |

| PCI Device ID       | 1533                                  |

| PCI Address         | 08:00:00                              |

| Link Status         | [Connected]                           |

| MAC Address         | XX:XX:XX:XX:XX:XX                     |

| Virtual MAC Address | 00:00:00:00:00                        |

### 8.3.3 Security